Binary Ripple Counter – Operational Basics

1. Pendahuluan[kembali]

Dalam dunia elektronika digital, counter merupakan salah satu rangkaian dasar yang sangat penting dan luas penggunaannya, terutama dalam sistem penghitungan waktu (timing), pengukuran frekuensi, serta aplikasi pengendalian logika. Salah satu jenis counter yang paling sederhana namun efektif adalah binary ripple counter. Ripple counter bekerja dengan prinsip dasar pewaktuan berantai (cascaded timing), di mana perubahan keluaran dari satu flip-flop digunakan sebagai pemicu (trigger) bagi flip-flop berikutnya.

Untuk memahami cara kerja ripple counter secara mendalam, dapat digunakan contoh sebuah four-bit binary ripple counter yang dibangun dari J-K flip-flop negatif edge-triggered. Flip-flop jenis ini hanya merespons perubahan sinyal pada sisi jatuh (falling edge) dari pulsa clock. Masing-masing flip-flop dikonfigurasikan dalam mode toggle, sehingga akan membalikkan keadaan keluarannya setiap kali menerima pulsa pemicu.

Dalam konfigurasi ini, keluaran dari flip-flop pertama (Q0, LSB) digunakan sebagai sinyal clock bagi flip-flop kedua (Q1), dan seterusnya hingga flip-flop keempat (Q3, MSB). Karakteristik "ripple" muncul karena penundaan propagasi sinyal dari satu flip-flop ke flip-flop berikutnya, menghasilkan urutan penghitungan biner yang khas. Melalui analisis bentuk gelombang keluaran tiap flip-flop, dapat diamati bagaimana bit-bit biner tersebut berubah sesuai dengan pulsa clock yang masuk.

Dengan memahami dasar operasi ini, siswa atau praktisi dapat memperoleh pemahaman yang kuat mengenai prinsip kerja rangkaian logika sekuensial dan bagaimana sinyal-sinyal digital ditransmisikan dan diproses secara berurutan dalam sistem digital.

2. Tujuan [kembali]

- Mempelajari dan memahami konfigurasi rangkaian Cascading Counters menggunakan J-K flip-flop.

Memahami cara membuat dan menyimulasikan rangkaian Cascading Counters pada software Proteus

Mengetahui prinsip kerja dan aplikasi dari rangkaian Cascading Counters dalam sistem digital.

3. Alat dan Bahan [kembali]

1. Gerbang NOT

Gerbang NOT merupakan suatu jenis logic gates yang memiliki fungsi sebagai suatu pembalik, atau yang dikenal dengan istilah inverter. Dengan demikian, nilai yang merupakan hasil keluaran (output) yang didapatkan akan selalu bertolak belakang dengan input..

2. Gerbang NAND (Not AND)

Gerbang NAND adalah salah satu gerbang logika dasar dalam elektronika digital yang menghasilkan output yang bernilai kebalikan dari output gerbang AND. Artinya, output dari gerbang NAND akan bernilai rendah (0) hanya jika semua inputnya bernilai tinggi (1). Jika ada satu atau lebih input yang bernilai rendah, maka outputnya akan bernilai tinggi.

Logic probe adalah alat bantu elektronik yang digunakan untuk mendiagnosis dan menguji logika digital dalam rangkaian digital. Alat ini sangat berguna saat bekerja dengan IC logika (seperti flip-flop, counter, dll) untuk mengetahui apakah sebuah titik pada rangkaian memiliki logika tinggi (HIGH/1), logika rendah (LOW/0), atau berubah-ubah (pulsing/berosilasi).

4. Dasar Teori [kembali]

Ripple counter, juga dikenal sebagai asynchronous counter, adalah jenis penghitung biner digital yang terdiri dari beberapa flip-flop yang dikonfigurasi secara berantai (cascading). Dalam konfigurasi ini, keluaran dari satu flip-flop digunakan sebagai sinyal clock bagi flip-flop berikutnya, sehingga perubahan keadaan (toggle) terjadi secara bertahap seperti riak (ripple) air.

Salah satu implementasi umum dari ripple counter adalah dengan menggunakan J-K flip-flop yang dikonfigurasi dalam mode toggle, yaitu kondisi J = K = 1. Flip-flop yang digunakan bersifat negative edge-triggered, artinya perubahan keadaan hanya terjadi pada transisi dari logika tinggi ke logika rendah (HIGH-to-LOW) pada sinyal clock.

Sebagai contoh, pada four-bit ripple counter, terdapat empat flip-flop yang masing-masing menghasilkan output Q0, Q1, Q2, dan Q3. Q0 merupakan Least Significant Bit (LSB), sedangkan Q3 adalah Most Significant Bit (MSB). Setiap kali clock utama mengalami transisi negatif, flip-flop pertama (Q0) akan berubah keadaan. Perubahan Q0 kemudian menjadi clock bagi flip-flop kedua (Q1), dan begitu seterusnya untuk Q2 dan Q3.

Rangkaian ini menghasilkan 16 keadaan biner berbeda (0000 sampai 1111), yang kemudian diulang kembali ke keadaan awal (0000) pada siklus clock ke-17. Secara umum, dengan N buah flip-flop, ripple counter dapat menghitung hingga 2ⁿ keadaan, dan akan melakukan reset otomatis ke kondisi awal setelah itu.

Selain digunakan untuk menghitung, ripple counter juga berfungsi sebagai pembagi frekuensi. Output setiap flip-flop memiliki frekuensi setengah dari input clock-nya. Artinya:

-

Q0 menghasilkan frekuensi f/2

-

Q1 menghasilkan frekuensi f/4

-

Q2 menghasilkan frekuensi f/8

-

Q3 menghasilkan frekuensi f/16

Dengan demikian, ripple counter dapat berperan sebagai rangkaian divide-by-2ⁿ, yang merupakan aplikasi penting dalam bidang sistem digital seperti pewaktuan (timing), pembuatan sinyal frekuensi rendah, dan sinkronisasi sinyal.

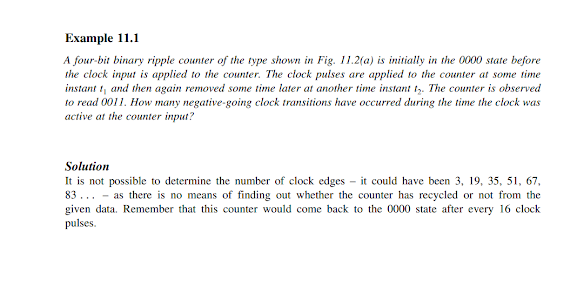

Soal 1

Sebuah 4-bit ripple counter menggunakan J-K flip-flop yang disambungkan sebagai toggle flip-flop. Jika semua flip-flop awalnya dalam keadaan LOW (0), maka apa output (Q3 Q2 Q1 Q0) setelah menerima 3 pulsa clock?

A. 0001

B. 0011

C. 0010

D. 0100

✅ Jawaban: C. 0010

Penjelasan:

Setiap pulsa clock memicu flip-flop pertama (Q0). Karena konfigurasi ripple, perubahan propagasi ke Q1, Q2, dst.

Urutan:

-

CLK 1 → Q0 toggle → 0001

-

CLK 2 → Q0 toggle → Q1 toggle → 0010

-

CLK 3 → Q0 toggle → 0011

Tapi soal minta setelah 3 pulsa clock, maka hasil = 0011, jadi:

⛔ Koreksi jawaban: ✅ Jawaban: B. 0011

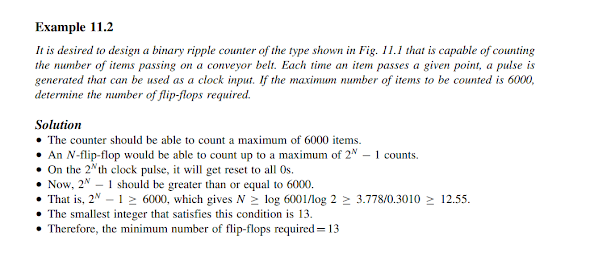

Soal 2

Apa fungsi utama dari ripple counter jika dilihat dari output frekuensinya?

A. Menyimpan data sementara

B. Mengalikan frekuensi input

C. Membagi frekuensi input

D. Mendeteksi kesalahan logika

✅ Jawaban: C. Membagi frekuensi input

Penjelasan:

Setiap flip-flop dalam ripple counter membagi frekuensi input-nya menjadi setengahnya, sehingga fungsi utama adalah sebagai pembagi frekuensi (frequency divider).

Soal 3

Jika frekuensi clock input ke sebuah 4-bit ripple counter adalah 16 kHz, maka berapa frekuensi keluaran pada Q3?

A. 8 kHz

B. 2 kHz

C. 1 kHz

D. 500 Hz

✅ Jawaban: D. 1 kHz

Penjelasan:

Q3 adalah output dari flip-flop keempat → f = 16 kHz / 2⁴ = 1 kHz

5. Percobaan [kembali]

a) Prosedur[kembali]

Persiapan Alat dan Software:

- Siapkan perangkat lunak Proteus (atau breadboard jika eksperimen dilakukan secara fisik).

Komponen yang dibutuhkan:

- 4 buah J-K flip-flop (misalnya IC 7476)

- Clock generator (atau pulse switch)

- Logic probe (atau LED indikator)

- Power supply (+5V)

- Ground (GND)

-

Rangkai Rangkaian Binary Ripple Counter:

Hubungkan keempat flip-flop secara berantai:

Clock pertama (CLK) ke flip-flop pertama.

-

Output Q dari flip-flop pertama ke clock input flip-flop kedua.

-

Lanjutkan sambungan ini hingga flip-flop keempat.

-

Set J dan K dari semua flip-flop ke logika HIGH (1), agar berfungsi sebagai toggle.

-

Hubungkan output Q0, Q1, Q2, dan Q3 ke LED atau logic probe untuk memantau perubahan status.

-

Setel Awal Flip-Flop:

Pastikan semua flip-flop berada pada kondisi awal LOW (0). Jika tersedia, gunakan tombol reset (CLR) untuk menyetel ulang.

-

Jalankan Clock:

Aktifkan clock generator dengan frekuensi lambat (misal 1 Hz agar mudah diamati).

-

Amati setiap perubahan output Q0 hingga Q3 setiap kali clock mengalami transisi dari HIGH ke LOW.

b) Rangkaian Simulasi dan Prinsip Kerja [kembali]

Ripple counter bekerja berdasarkan prinsip kerja flip-flop yang terhubung secara berantai (cascading), di mana output dari satu flip-flop digunakan sebagai input clock untuk flip-flop berikutnya. Dalam konfigurasi ini, semua flip-flop diset sebagai toggle flip-flop (J = K = 1) dan hanya merespons pada transisi negatif (HIGH ke LOW) dari sinyal clock karena menggunakan negative edge-triggered J-K flip-flop.

Setiap flip-flop akan mengubah keadaan keluarannya (toggle) setiap kali menerima satu pulsa clock. Output Q0 akan toggle setiap pulsa clock masuk, Q1 akan toggle setiap 2 pulsa clock, Q2 setiap 4 pulsa, dan Q3 setiap 8 pulsa. Dengan demikian, rangkaian ini menghasilkan output yang berfungsi sebagai penghitung biner dari 0000 hingga 1111 (0–15) dan juga berperan sebagai pembagi frekuensi dari sinyal clock.

c) Video Simulasi [kembali]

6. Download File [kembali]

- Download rangkaian 11.2 klik disini

- Download video rangkaian 11.2 klik disini

- Download datasheet Resistor [disini]

- Download datasheet clock [disini]

- Download datasheet seven segment [disini]

- Download datasheet Op Amp [disini]

- Download datasheet IC 4013 [disini]

- Download datasheet IC 74247 [disini]

- Download datasheet Potensiometer [disini]

- Download datasheet Resistor [disini]

- Download HTML disini

Comments

Post a Comment